Grant Agreement number: 288574

Project acronym: vIrtical

Project title: SW/HW extensions for virtualized heterogeneous multicore platforms

Seventh Framework Programme

Funding Scheme: Collaborative project

FP7 -ICT -2011-7

Objective ICT-2011.3.4 Computing Systems

Start date of project: 15/07/2011 Duration: 36 months

**D 1.1** *Acceleration, memory system opportunities, and virtualization requirements in selected industrial applications*

#### Due date of deliverable: Month 12

Actual submission date: Month 14

Organization name of lead beneficiary and contributors for this deliverable: THALES, UPV, UNIBO, STM

Work package contributing to the Deliverable: WP1

|    | Dissemination Level                                                                   |   |  |  |

|----|---------------------------------------------------------------------------------------|---|--|--|

| PU | Public                                                                                | Х |  |  |

| PP | Restricted to other programme participants (including the Commission Services)        |   |  |  |

| RE | Restricted to a group specified by the consortium (including the Commission Services) |   |  |  |

| СО | Confidential, only for members of the consortium (including the Commission Services)  |   |  |  |

#### **APPROVED BY:**

| Partners | Date               |

|----------|--------------------|

| ALL      | September 4th 2012 |

# Index

| Index                                                                                        |    |

|----------------------------------------------------------------------------------------------|----|

| Abstract                                                                                     |    |

| Glossary (Please ensure that any acronyms used are clearly explained)                        |    |

| Full Description of Deliverable content                                                      |    |

| 1. Introduction                                                                              |    |

| 2. Analyzed Applications                                                                     | 4  |

| 2.1. Applications for consumers                                                              | 4  |

| 2.1.1. Android                                                                               |    |

| 2.2. Applications for telephony, data clustering and cryptography                            | 6  |

| 2.2.1. Asterisk                                                                              | 6  |

| 2.2.2. KCluster                                                                              | 7  |

| 2.2.3. OpenSSL                                                                               | 8  |

| 2.3. Applications for Vision and Image Processing                                            | 8  |

| 2.3.1. SIFT                                                                                  |    |

| 2.3.2. SURF                                                                                  | 9  |

| 2.3.3. FAST + BRIEF                                                                          | 10 |

| 3. Acceleration opportunities                                                                | 11 |

| 3.1. Acceleration opportunities for telephony, data clustering and cryptography applications |    |

| 3.1.1. Asterisk                                                                              |    |

| 3.1.2. KCluster                                                                              |    |

| 3.1.3. OpenSSL                                                                               |    |

| 3.2. Acceleration opportunities for Vision applications                                      |    |

| 3.2.1. Architecture Specific Optimizations                                                   |    |

| 3.2.2. Coarse-Grained Thread-Level Parallelization                                           |    |

| 3.2.3. Fine-Grained Data-Level Parallelization                                               |    |

| 4. Memory system opportunities                                                               |    |

| 4.1. Analysis Methodology                                                                    |    |

| 4.1.1. Target System                                                                         |    |

| 4.1.2. Simulation Tools                                                                      |    |

| 4.1.3. Trace Acquisition Methodology                                                         |    |

| 4.1.4. Applications                                                                          |    |

| 4.2. Sharing patterns analysis                                                               |    |

| 4.2.1. Analysis Results                                                                      |    |

| 4.3. Compression Opportunities                                                               | 41 |

| 4.3.1. Analysis Results                                                                      |    |

| 5. Virtualization Requirements                                                               |    |

| 5.1. Domain requirements                                                                     |    |

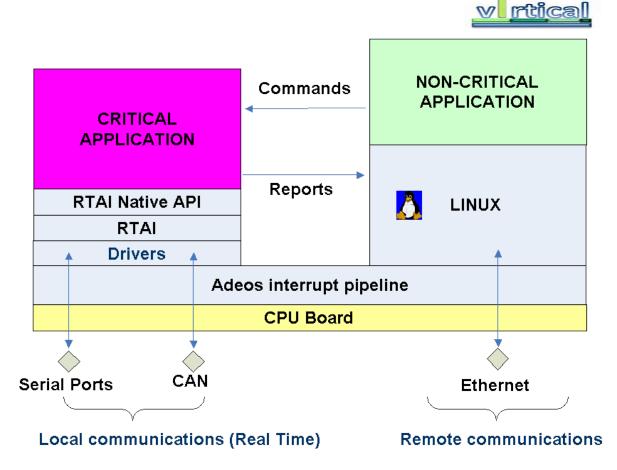

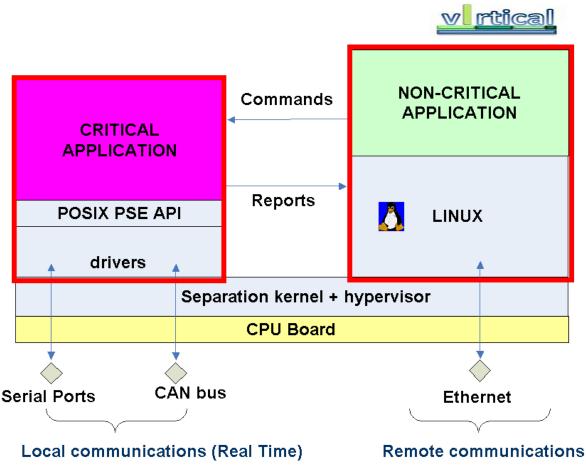

| 5.1.1. Telecommunications                                                                    |    |

| 5.1.2. Consumer Electronics                                                                  |    |

| 5.1.3. Automotive and Vetronics                                                              |    |

| 5.1.4. Transportation                                                                        |    |

| 5.1.5. Avionics                                                                              |    |

| 5.2. Technical requirements                                                                  |    |

| 5.2.1. Isolation between compartments                                                        |    |

| 5.2.2. Communications between compartments                                                   |    |

| 5.2.3. Resource sharing and reservation among compartments                                   |    |

| 5.2.4. Static and dynamic resource allocation for compartments                               |    |

| 5.3. Non-functional requirements                                                             |    |

| 5.3.1. Fault tolerance                                                                       |    |

| 5.3.2. Security                                                                              |    |

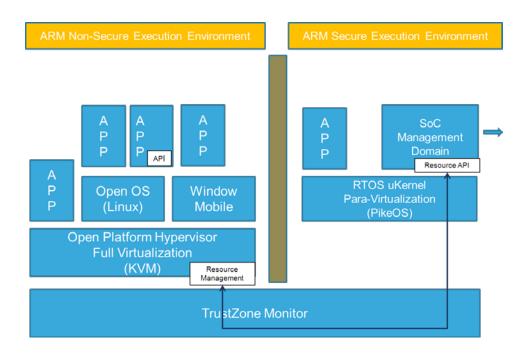

| 5.3.3. Co-existence of full virtualization and para-virtualization                           |    |

|                                                                                              | 00 |

| . 68 |

|------|

| . 68 |

| . 69 |

| . 70 |

|      |

# Abstract

Embedded devices are becoming more and more present everywhere. Moreover mobile devices are becoming also more computationally powerful. These embedded architectures present new challenges since they execute several applications that must preserve security, allow sharing information in a coherent way, to be scalable and provide the required levels of performance, while at the same time they must be power efficient.

In this context, the virtical project focuses on these challenges and as a starting point, it tackles the characterization of applications targeted for the hardware platform developed in the project, that is, a heterogeneous multicore SoC. For this purpose several typical industrial applications and some computer vision kernels have been selected for characterization. From these applications, we have first analyzed acceleration opportunities in order to identify which computational kernels are best candidates for acceleration. Second, we have analyzed memory sharing patterns in order to exploit them to make the coherence protocols more scalable and power-efficient. Moreover we also have analyzed the compression opportunities offered by data moving between memory and cores in order to design a more power-efficient platform. Finally we also identify virtualization opportunities of industrial applications. As we show in this deliverable in the next sections, industrial applications exhibit acceleration, memory and virtualization opportunities that taken into consideration will enable the design of more efficient, scalable and secure heterogeneous multicore devices.

#### **Glossary** (Please ensure that any acronyms used are clearly explained)

CC: Common Criteria CV: computer vision EAL: Evaluation Assurance Level NoC: Network on Chip PBX: private branch exchange QoS: Quality of Service SoC: System on Chip VoD: Video-on-Demand VoIP: Voice over IP

# **Full Description of Deliverable content**

# 1. Introduction

The use of computers has been extended to most areas of our everyday life. Embedded devices are becoming more and more present everywhere. In the Internet, computational load is moving from computers to servers, being clusters a very popular solution to provide the required computing power. Moreover mobile phones, PDAs and in general mobile devices are becoming also more computationally powerful since they are intended to perform complex computations locally. These embedded architectures present new challenges since they execute several applications that must preserve security, allow sharing information in a coherent way, to be scalable and provide the required levels of performance, while at the same time they must be power efficient.

In this context in the vlrtical project, we tackle these challenges, and as a starting point, we characterize applications targeted for the hardware platform developed in the project, that is, a heterogeneous muticore SoC. For this purpose Thales has provided us with a set of application examples covering the industrial needs. Moreover, some computer vision (CV) kernels have been also selected since scientific and industrial communities are showing a growing interest in developing this kind of algorithms on embedded systems. All the applications are described in Section 2. From these applications, we have first analyzed in Task 1.1 acceleration opportunities in order to identify which computational kernels are best candidates for acceleration (Section 3). Second in Task 1.3, we have analyzed memory sharing patterns (Section 4.2) in order to identify opportunities to be exploited to make the coherence protocols more suitable for embedded devices being more scalable and power-efficient. Moreover, also in Task 1.3 we have also analyzed the compression opportunities (Section 4.3) offered by data moving between memory and cores in the industrial applications, in order to design compression techniques that enable a more power-efficient platform. Finally, in Task 1.1 we have also identified virtualization opportunities of industrial applications.

# 2. Analyzed Applications

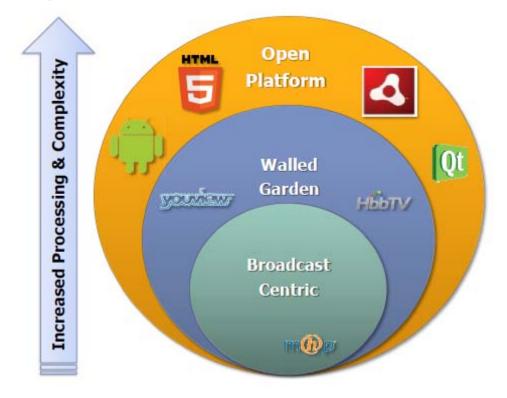

# 2.1. Applications for consumers

Smart set-top boxes often garner less attention than other connected CE devices like TVs and game consoles. However, there is a growing interest in generic Android based set-top boxes. The changing consumer landscape, however, could present a window of opportunity for smart set-top boxes as more consumers allocate entertainment budget, both monetary and time, to streaming media via the set top box. Today, we start to see on the market some examples how mobile contents could be streamed via a set top box or how to play android games in a set top box.

## 2.1.1. Android

From Wikipedia, Android is a Linux-based operating system for mobile devices such as smartphones and tablet computers. It is developed by the Open Handset Alliance, led by Google. Today, Android has a large community of developers writing applications ("apps") that extend the functionality of the devices. Developers write primarily in a customized version of Java. Apps can be downloaded from third-party sites or through online stores such as Google Play (formerly Android Market), the app store run by Google. In June 2012, there were more than 600,000 apps available for Android, and the estimated number of applications downloaded from Google Play was 20 billion.

The software stack is divided in four different layers, which include 5 different groups:

- The application layer

- The Android software platform will come with a set of basic applications like browser, email client, SMS program, maps, calendar, contacts and many more. All these applications are written using the Java programming language. It should be mentioned that applications can be run simultaneously, it is possible to hear music and read an email at the same time. This layer will mostly be used by commonly cell phone users.

- The application framework

- An application framework is a software framework that is used to implement a standard structure of an application for a specific operating system. With the help of managers, content providers and other services programmers it can reassemble functions used by other existing applications.

- The libraries

- The available libraries are all written in C/C++. They will be called through a Java interface. These includes the Surface Manager (for compositing windows), 2D and 3D graphics, Media Codecs like MPEG-4 and MP3, the SQL database SQLite and the web browser engine WebKit.

- The runtime

- The Android runtime consists of two components. First a set of core libraries, which provides most of the functionality available in the core libraries of the Java programming language. Second the virtual machine Dalvik, which operates like a translator between the application side and the operating system. Every application which

runs on Android is written in Java. As the operating system is not able to understand this programming language directly, the Java programs will be received and translated by the virtual machine Dalvik. The translated code can then be executed by the operating system.

- The kernel

- A customized version of the Linux Kernel will be used by Android for its device drivers, memory management, process management and networking.

Android as shown in section 5.1.2 will be used in set top box or TV to open up the environment to the end users. This will allows the end user, on top of existing functionalities, to stream data, download apps, play games, use IP telephony etc. In this context, virtical project will explore during the second year of the project how to improve android performances by offloading code to the GPPA component or by using some compression techniques

## 2.2. Applications for telephony, data clustering and cryptography

Thales Communications & Security has provided 3 applications from 3 different domains:

- 1. Asterisk: PBX used in telephony.

- 2. KCluster: data clustering used in speech recognition.

- 3. OpenSSL: cryptography used in secure communications.

#### 2.2.1. Asterisk

Asterisk is historically the first open source private branch exchange (PBX) for IP (Internet Protocol), digital and analogue interfaces. Asterisk was created in 1999, first version was released in 2004. The latest version is 10.0 released on 15 December 2011.

Asterisk offers a large set of PBX features like call forwarding, callee identification, conferences and voicemail as well as a variety of call center and operator grade services such as interactive voice response, text-to-speech and external call management via integrated APIs (Application Programming Interface). Many VoIP (Voice over IP), analogue and ISDN protocols are supported together with most of standard codecs. Asterisk is available under dual license: a GPL (General Public License) and a proprietary software license allowing personalized closed source distributions. It runs on Linux on x86 and PPC (Power PC) architectures. It supports many telephony interface cards allowing its use as a gateway and media compression cards allowing video and voice codec real-time conversion. It is maintained by Digium Incorporation based in Alabama, USA.

Asterisk is widely used by Thales Communications & Security, mainly for test purposes, but also as a gateway.

Asterisk based call generators are used during the validation of Thales telecommunication products. Automated test framework executes configured scenario and reports number of dropped or failed calls, average call establishment time, voice quality etc. Thanks to numerous Asterisk's interfaces, this test tool can be used on VoIP as well as analogue interfaces.

Asterisk is also used in several Thales gateways. Asterisk's features allow its use in two types of gateway: VoIP/analogue and VoIP/ISDN gateways. An example of a VoIP/analogue gateway is an integration of radio equipment in a VoIP network, where it's necessary to convert an analogue radio interface to an IP based one. Thales's VoIP/ISDN gateways integrate client specific value added services like QoS management.

Efficiency and scalability of Asterisk on multicore embedded platforms is of prime interest for Thales, as well as the capability to handle power-efficient switches between a large number of connections occurring in seldom cases and a small number of connections occurring at all times.

#### 2.2.2. KCluster

At the heart of the KCluster application there is the well-known K-Means core algorithm which is done in one single stage. The variant here proposed does the split in two-stages in order to allow for parallelization of multiple K-Means algorithms in the second stage. K-Means is an algorithm designed to iteratively build a representative codebook from a training set of multidimensional data. The resulting codebook consists of a set of centroids, optimized to minimize a global distortion. The global distortion is computed as the cumulated distortion over all the training vectors using a nearest-neighbor criterion to select the representative centroid for each data vector.

#### **K-Means principle**

- Initialization step: before entering the k-Means iterative optimization process, the centroids should be initialized. Various methods can be used for initialization depending on the available a priori information on the data. Here we only provide two types of initialization: random selection of vectors in the training set, and selection of the vectors which are the closest to the global mean of the training set.

- Classification step: from an iteration to the other, once the centroids are updated (or initialized), all the training vectors are classified according to a nearest-neighbor rule. The training set is therefore partitioned in K classes associated to the corresponding K centroids.

- 3. Update step: once all the training vectors have been classified, the centroids are updated using the vectors in the corresponding class. The resulting codebook can then be re-optimized by going back to step 2), or considered as the final codebook depending on the termination step.

- 4. Termination step: the distortion is calculated as the cumulated distortion over all classes. One typical termination criterion is to stop the iterative optimization, when the relative distortion improvement is below a predefined threshold.

# 2.2.3. OpenSSL

OpenSSL is a well-known suite of open-source library and tools implementing cryptographic algorithms used for authentication and secure data transfers over networks. It is used by many services such as https and ssh. As indicated by its documentation, it implements the following cryptographic functions:

- Creation of RSA, DH and DSA key parameters,

- Creation of X.509 certificates, CSR and CRL,

- Calculation of message digests,

- Encryption and decryption with ciphers,

- SSL/TLS client and server tests,

Handling of S/MIME signed or encrypted mail.

## 2.3. Applications for Vision and Image Processing

Scientific and industrial communities are showing a growing interest in developing Computer Vision (CV) algorithms on high-end embedded systems. However, CV algorithms are well known for their high complexity and for being very resource-demanding. CV processing is indeed a computation-intensive task, dealing with huge amounts of data (an image can count several millions of pixels/bytes) and performing a large number of repetitive calculations over the whole image data set or part of it. Low-level data processing, like pixel-based operations, requires a large number of memory transactions and can quickly become a bottleneck if the system architecture is not tailored to such a kind of processing. Furthermore, higher-level algorithmic tasks (e.g., segmentation or recognition) can require complex iterative or recursive mathematical kernels that are quite demanding in terms of computational power. This is especially true in the embedded domain, where the complexity of processing nodes is limited by several constraints like power consumption, size and cost.

Accelerating those key computational kernel is thus paramount to speeding-up the execution time of more complex applications such as object motion tracking, object recognition and similar. We have identified three core kernels that are used by several vision applications to extract significant features from images:

- 1. SIFT (Scale-Invariant Feature Transform)

- 2. SURF (Speeded-Up Robust Features)

- 3. FAST + BRIEF (corner detection).

These kernels are used as a basic step in many applications in the field of computer vision: they work on raw images, and managing large amounts of raw data they basically turn out to be computation bottlenecks.

#### 2.3.1. SIFT

SIFT [Bay08] is an algorithm that detects and describes image features. The computed features are mainly invariant to image scaling and rotation, and partially to change in illumination and camera viewpoint. SIFT uses a cascade filtering approach: it looks for some distinctive points (keypoints) in the image, then most of the candidate points are discarded at an early computation stage, in order to skip computationally intensive operations. The first stage of the algorithm creates a Gaussian pyramid that is a set of images which are derived from the original one applying a sequence of downsampling, upsampling and blurring filters. The algorithm provides three main configuration values to define this gaussian space, which are the number of octaves, the scale of first octave and the number of layers. Each octave is characterized by a different image scale, and default parameters imply a variation from twice the original size (octave scale 1) to one fourth of the original size (octave scale 2). The layers are the images actually contained in each octave: each layer, from 0 to 2 in the default implementation, corresponds to a increasing sigma value for gaussian blurring filter. The second stage computes the Difference of Gaussians (DoG) between adjacent layers in the same octave, and also the gradient of images, which is computed for each octave and layer. The third stage is the keypoint localization: local estrema in the DoG images are selected as candidate keypoints, considering neighboring pixels in both the selected image and the adjacent ones (which have been computed by the same layer image). Keypoints are filtered to remove edges, as they are redundant, and finally a non-maxima suppression is performed. The fourth stage assigns an orientation to each keypoint (sometimes more than one), using the local values of the gradient in the point area. The last stage is the creation of keypoint descriptors. The 16x16 region around each keypoint is described using a statistical analysis of local gradient orientations: orientation histograms are computed considering 4x4 subregions and 8 bins, then they are packed into 128-entries descriptors. The descriptors are finally normalized with the aim to minimize the effects of change in illumination. SIFT is one the most accurate algorithms for feature detection, but at the same time it is quite slow, so it is currently considered to be unsuitable for real-time applications, unless we consider small images or need a greater accuracy.

## 2.3.2. SURF

SURF **[Cal10]** is a detector and descriptor algorithm. Its approach is similar to SIFT but SURF uses faster techniques, and in some cases it is also more robust than SIFT. The detector stage is based on the determinant of a Hessian matrix, and considers both position and scale. Hessian matrices are computed by means of discrete box filters, that approximate second order Gaussian derivatives and can be computed using integral images. SURF uses 9x9 box filters at the lowest scale, referred as scale 1.2 (1.2 is the sigma parameter of the Gaussian filter). The scale space is analyzed by upscaling the filter size using bigger masks: this operation has a constant cost when using integral images, which in general enable fast computation of box type

convolution filters for big kernel sizes. The scale space is divided into octaves, which are subdivided into a constant number of levels. The default parameters of the algorithm provide 4 octaves, and 4 levels per octave.

The minimum increase of the mask size for two adjacent levels corresponds to 6 pixels, in order to guarantee a good Gaussian approximation. At the first octave, filters with sizes 15x15, 21x21 and 27x27 are applied. For each new octave, the filter size is doubled: the filter sizes for the second octave are 15x15, 27x27, 39x39, and 51x51. The last octave uses 51x51, 99x99, 147x147 and 195x195 kernels. To reduce the sampling intervals for the extraction of the interest points, the sampling step is doubled at each new octave, with minimum loss of accuracy.

In order to localize interest points, the maxima of calculated determinants are interpolated in scale space, and then a non-maximum suppression in a 3x3x3 neighborhood is applied.

The descriptor phase of SURF is similar to SIFT: a main orientation is first computed for the keypoint, and then orientation statistics are extracted for a region centered on the point itself. The size of this window is 20 times the image scale value, and it is divided in 4x4 subregions, each one internally divided in 4x4 areas. SURF computes orientations using Haar wavelet responses, which are invariant to changes in illumination and contrast. The final keypoint descriptor vector contains 64 elements.

#### 2.3.3. FAST + BRIEF

FAST **[Ros10]** is a corner detection algorithm. It analyzes all points in the image, and compares the intensity value of each point p with all the sixteen points on the circle of radius 3 and center p; p is classified as a corner if there exists a set of contiguous pixels within the circle that are all brighter (minimum) or darker (maximum) of p (with a tolerance threshold). The number of contiguous pixels and the threshold value are both algorithm parameters; typical values are respectively 9 and 20.

All the versions of FAST assign a score to each detected corner, in order to enable a subsequent non-maximal suppression stage, with the aim to filter the corners which have an adjacent corner with higher score. Even if it can be used as a feature detector, FAST does not provide a step to generate keypoint descriptors. Nonetheless, extracted features can be described using a companion algorithm: a typical example is BRIEF, which produces compact binary descriptors.

BRIEF **[DBw**<sup>3</sup>] is an algorithm that computes keypoint descriptors using a method that produces efficient bit strings. The algorithm computes a small number of pairwise comparisons on a image patch centered on the keypoint, and then creates a bit vector as the final result of all the comparisons related to the same keypoint. This vector is finally packed in a bit string. At each step, BRIEF smooths the current image patch with a Gaussian filter, in order to reduce noise sensitivity and increase the stability and repeatability of the descriptors. The numbers of

pairwise comparisons considered by the authors (corresponding to a binary string of 16, 32 or 64 bytes) yield a good trade-off among speed, storage efficiency and recognition rate.

# 3. Acceleration opportunities

In this section we analyze the acceleration opportunities of the target applications described in the previous one.

The target platform template considered in the virtical project consists of an ARM-based host subsystem, plus accelerators of different nature (i.e., a programmable manycore, the GPPA, plus HW functional units, HWPUs), which can deliver tremendous peak performance, given that the target application can exploit it. In this section of the document we investigate the potential for different approaches to accelerating the target applications. We consider three different approaches, which are currently being adopted by vendors and/or research institutes

- Architecture Specific Optimizations: this methodology consists of assessing the acceleration opportunities for an implementation of the target algorithm that is optimized to run on the ARM host processor only, taking advantage of specific architectural features (e.g., SIMD engine).

- Coarse-Grained Thread-Level Parallelization: this approach aims at assessing the acceleration opportunities for an implementation of the target algorithm that parallelizes the workload among the small number of available cores in a typical ARM multi-core host subsystem. Coarse-grained threads are identified as a parallel unit of work from the application.

- 3. Fine-Grained Data-Level Parallelization: this methodology explores the potential for accelerating the target application on a large number of threads, by offloading it onto the GPPA. Thus we consider a different parallelization scheme which is fine-grained enough to keep busy a very large number of cores. We leverage loop-level parallelism to generate several fine-grained threads.

In particular, approaches 1 and 2 are suitable for the industrial applications described in Section 2.1, as explained in the following sections. Computer vision algorithms, on the other hand, are characterized by a remarkable workload, in particular when high definition images are considered. The traditional target of CV libraries is the desktop computing environment. Since embedded devices have not the same computing capabilities of desktop mainstream processors, the execution of such algorithms on mobile platforms often presents unsatisfying performance. However, CV workloads often exhibit fine-grained (i.e., pixel-level) parallelism, which makes them a suitable candidate for acceleration on the GPPA (approach 3).

We will thus describe the acceleration approaches for the two categories of applications in the two following sections.

# 3.1. Acceleration opportunities for telephony, data clustering and cryptography applications

#### 3.1.1. Asterisk

As introduced in Section 2.1.1, Asterisk offers several PBX features for telephony services. New voice calls are handled by creating additional threads, thus it becomes straightforward to manage execution of multiple threads in parallel. Clearly, the degree of parallelism is directly dependent on the number of simultaneous calls occurring at the Asterisk host, thus we can only consider exploiting coarse-grained task-level parallelism for this application. This type of parallelism is well suited to run entirely on the host ARM system. A tasking programming model (e.g., OpenMP task directives) can be used to specify dynamically the creation of additional parallelism from the application.

## 3.1.2. KCluster

The KCluster application heavily relies on KMeans-based data clusterization. There are many approaches in literature discussing parallelization of KMeans for different systems (for a good survey see **[Zha06]**). The algorithms lend itself to different partitioning granularities: task parallel, data parallel and a mix of the two. In order to allow for parallelization of the KCluster application, we provide the following modified version of KMeans.

#### **Modified K-Means**

In the provided implementation, we consider a clustering algorithm combined several K-Means processes. A primary codebook (size L0) is first optimized on the whole training set. Then for each resulting centroid, we consider the set of vectors in the corresponding class as a new training set for secondary codebook (size L1). The secondary codebooks are iteratively optimized, and training data are re-allocated at the end of each iteration.

#### Parallelization

The optimization of the L0 secondary codebooks (of size L1) can be parallelized using a multicore processing platform. Generally the number of core processing units will be less than the number of L0 of codebooks, and the allocation of each optimization process should be done dynamically, since the duration of each optimization process can be different. It is approximated in the example code by the required number of iterations, in order to provide an example of dynamic allocation to the different cores.

This partitioning scheme, mostly task-based, is convenient for execution on the ARM subsystem. The load imbalance issue can be easily addressed by dynamically allocating parallel tasks to available processor, rather than statically determining a workload partitioning scheme.

# 3.1.3. OpenSSL

Cryptographic algorithms can be accelerated by using co-processing resources such as SIMD engines or specific cryptographic devices such as those present in PowerQUICC processors. Within the vIrtical project the first approach can be implemented by leveraging ARM NEON extensions. Dedicated HW blocks like those from the second approach could also be considered by implementing a specific HWPU (HW Processing Unit, see D1.2).

Also, a few approaches to parallelization of a class of encryption algorithms (AES, Rijndael) on many-core devices (i.e., GPUs) are available in literature **[Le10]**, which promise speedups of up to 7x, and which could be considered as a guideline to accelerating such algorithms on the GPPA in the vIrtical project.

More information on OpenSSL is available at www.openssl.org

## 3.2. Acceleration opportunities for Vision applications

While in literature there are several approaches to parallelizing applications for data clustering or cryptography, discussed in the previous section, for computer vision kernels there is less previous work available, which calls for a more detailed analysis. The source code for the computational kernels described in Section 1.2 is available from the open-source OpenCV (Open Source Computer Vision) library **[Stu11]**. OpenCV is a CV-oriented, cross-platform programming library, widely used by both academic and industrial partners. A pre-parallelized version of these kernels, which we use for approach 2 from the list above, comes from the MEVBench suite from University of Michigan **[Cle11]**.

The presentation of our study is divided into three independent sections, each one related to a different approach. To conduct our preliminary studies and to validate the above-mentioned methodologies prior to the definition and the availability of the virtical platform, we use the following approaches:

- A. To estimate the behavior of code optimization strategies meant for the host system we use a Qualcomm DragonBoard [OCVw<sup>3</sup>] as a hardware platform. The DragonBoard is an advanced developer board, featuring a Snapdragon S3 APQ8060 SoC, which shares the following key architectural characteristics with the host system of the virtical platform:

- An ARM-based dual-core host system, based on the same ARMv7 ISA of the Cortex A15

- Support for the signal processing-oriented NEON instruction set extensions and floating-point VFPv3 extensions (the VeNum media processing engine)<sup>1</sup>.

- An Android-ready SDK, which allows us to readily execute OpenCV codes

<sup>&</sup>lt;sup>1</sup> Qualcomm's NEON data paths are 128-bits wide. Since the ARM NEON is 64-bits wide, the Snapdragon S3 VeNum can issue the equivalent of two NEON instructions in parallel.

Table 1 summarizes the main architectural parameters for the Snapdragon S3 SoC.

B. To estimate acceleration opportunities for parallelization approaches leveraging programmable manycores (i.e., the GPPA – approach 3 from the list above) we either use a in-house, SystemC simulator of a cluster of the GPPA (see D1.2) or commodity GPU card. Specifically, we use a NVIDIA GeForce GTX 480 on a desktop machine equipped with a Intel Core i7920 CPU @ 2.67 GHz and 6GB DDR3.

| Sn               | apdragon S3            |

|------------------|------------------------|

| Processor        |                        |

| CPU              | Dual Scorpion CPU      |

| Frequency        | 1.2  GHz,  per core    |

| L1 Cache $(I/D)$ | (32KB / 32KB) per core |

| L2 Cache         | 512 KB Shared          |

| Memory           |                        |

| Frequency        | LPDDR2-333 (ISM)       |

| Memory Size      | 1GB                    |

Snapdragon S3

Table 1: Snapdragon S3 SoC hardware parameters.

#### 3.2.1. Architecture Specific Optimizations

The first set of experiments is aimed at assessing the acceleration opportunities for architecture-specific optimizations on the host processor. We consider three different implementations of the FAST benchmark (see FAST + BRIEF):

- OpenCV: the original algorithm, contributed to OpenCV by the author, Edward Rosten. The algorithm has been substituted in OpenCV 2.3.1 with the optimized version (see below).

- **Rosten**: Machine-generated code, optimized for speed **[Ros10]**. It consists of an heuristic procedure derived from a machine learning tree.

- FastCV: the FAST algorithm from the FastCV library. FastCV [QDNw<sup>3</sup>] is a proprietary vision library distributed by Qualcomm providing a mobile-optimized computer vision library which includes the most frequently used vision processing functions for use across a wide array of ARM-based mobile devices. FastCV is designed for efficiency on all ARM-based processors, but is tuned to take advantage of Qualcomm's Snapdragon processor (S2 and above). In particular it uses vectorial instructions to perform multiple comparisons per cycle.

**OpenCV** and **Rosten** algorithms are compiled with the g++ compiler included in the standard NDK toolchain, with instruction set ARMv7, NEON support disabled and optimization level -O2. The **FastCV** library is distributed in binary form and can execute in two distinct operative modes: Performance mode (1), which enables the SIMD unit, and Low Power mode (2), which only runs on the processor.

ntina

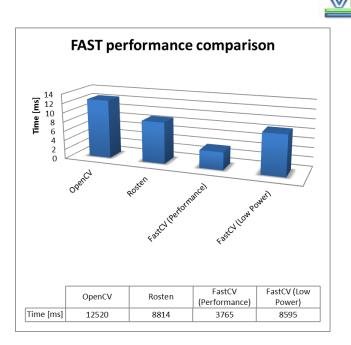

Fig. 1: Comparison of FAST implementations.

*Fig. 1* depicts the execution times (in milliseconds) of each FAST implementation. On the bottom part of the figure we report execution times in a table.

The results show that exploiting processor architecture-specific optimizations, notably the SIMD engine, the algorithm execution time can be sped-up up to 2.34 w.r.t. the standard version.

# 3.2.2. Coarse-Grained Thread-Level Parallelization

Besides using SIMD acceleration, another opportunity for improving the performance of the target applications on the host subsystem is parallelization. The small number of processors available on the multi-core processor clearly limits the number of threads that it is possible to exploit in the parallelization strategy. A parallel implementation of the target algorithms for general-purpose processors is provided in the freely-available, open-source MEVBench suite **[Cle11]**. We tuned the implementation of SIFT, SURF and FAST to run on Android systems. We consider a test image scaled in three different sizes:

- Small (352x288 pixels): 101376 pixels that require 2376 KB in RGB format and 792 KB in greyscale. 169 KB in PNG format. It is a standard size for mobile phone videos and images produced by very low-resolution digital cameras.

- Medium (640x480 pixels): 307200 pixels that require 7200 KB in RGB format and 2400 KB in greyscale. 465 KB in PNG format. It is a standard VGA format.

- HD (1920x1080 pixels): 2073600 pixels that require 48600 KB in RGB format and 16200 KB in greyscale. 1915 KB in PNG format. It is a standard full high definition format for video streams.

Note that the last configuration could only be tested with the FAST + BRIEF algorithm, since both SIFT and SURF run out of memory during the experiments.

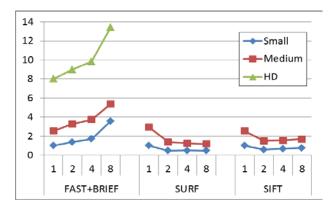

*Fig.* **2** shows the execution cycle scaling when parallelizing the various applications among an increasing number of threads (on the x-axis). Cycle count (on the y-axis) for the various configurations is normalized to the value for single thread, small image.

Fig. 2: Execution time (normalized) scaling for coarse-grained parallelization.

Regarding the FAST + BRIEF application, it is possible to see that there is basically no speedup when increasing the number of threads. This is due to i) the coordination phase which is extremely time consuming and not parallelizable thus dominating the Amdahl law sequential part and ii) the parallel part which adds coordination overhead (barrier) which increases with the number of threads.

Things change a little for the remaining two applications, where coarse-grained parallelization can achieve some speed-ups. For SIFT, the maximum speed-up is obtained with two threads (i.e., as many threads as cores). With this configuration the workload is balanced, and the coordination phase has a negligible impact. When more threads are considered the total overhead increases with no additional benefits derived by hiding memory latency by means of thread switching.

The last application, SURF, lacks a final complete coordination phase. In more detail, each thread performs feature extraction on a partially overlapping part of the image, and the same feature can be extracted multiple times: a final matching step is omitted, and the coordination phase reports the sum of the feature extracted. This is not a real issue, as a subsequent step may discard the repeated values if needed. SURF benefits from the overlapping between computation and memory transfers, due to a different algorithmic approach and a lighter coordination phase. Thread switching partially hides the effects of memory latency when we consider the medium-sized image, and consequently the speed-up increases when using more than two threads (more threads than cores).

Overall, the results for these preliminary experiments show that i) coarse-grained parallelization schemes intended for general-purpose processors may perform poorly on embedded devices,

due to different hardware (memory, synchronization) and ii) overall, increasing the number of software threads beyond the core count does not bring additional benefits, on the contrary it may slow down.

## 3.2.3. Fine-Grained Data-Level Parallelization

The experiments presented in the previous sections demonstrate that the speedup that can be achieved on the host subsystem by means of parallelization and exploitation of SIMD engines is limited. The platform template that we target in the vIrtical project can be equipped with a manycore programmable accelerator, the GPPA (General Purpose Programmable Accelerator). Clearly, the parallelization scheme that needs to be adopted to take advantage of the GPPA is very different from the one used in the MEVBenchs. Indeed, if the number of processing cores is small, parallelization can generally be coarse-grained, where the amount of work is high enough to keep the cores busy and can tolerate synchronization overheads among a small number of workers. However, the same parallelization approach is bound to provide poor results for higher processor counts. It is therefore important to evaluate the benefits of a parallel implementation that is designed with scalability in mind in this scenario. We present in the following the parallelization strategy for each of the benchmarks.

#### 3.2.3.1. SIFT

The SIFT algorithm consists of two main phases: features detection and feature description. We focus here on the most computation-intensive part, feature detection. A candidate feature (keypoint) is a pixel located at a specific image frequency scale that has either the minimum or the maximum value in relation to its neighborhood, defined by a 3x3 window located at the same scale space and at the upper and lower adjacent scales. The frequency band for each scale is obtained by using the difference of Gaussian (DoG) operation, which is computed by subtracting two identical images convolved by two different Gaussian kernels. Equation (1) defines the convolution operation for the first and the other subsequent scales, where I is the input image, K the Gaussian kernel and G the smoothed image.

$$G_0(x, y) = K_0(x, y) * I(x, y)$$

$$G_{s+1}(x, y) = K_{s+1}(x, y) * G_{s+1}(x, y)$$

(1)

Equation (2) defines the difference operation (DoG), where D is the resulting image at a specific frequency scale defined by the kernel values (s).

$$D_{i}(x, y) = G_{s+1}(x, y) - G_{s}(x, y)$$

(2)

Accepting a keypoint as a feature is evaluated through three functions: location refinement, contrast check and edge responses. The location refinement is performed as shown in Equation (3), where I is the pixel location vector (x; y; s) (coordinates <x;y> and scale s). This equation performs an interpolation operation with the pixels found inside of the keypoint's neighborhood

(26 pixels), with  $\omega$  added to the current keypoint position in order to produce its new location. The  $\omega$  offset is also used to compute the keypoint contrast. If the result is smaller than a userdefined threshold then the keypoint is rejected.

$$\omega = -\left(\frac{\partial^2 D}{\partial l^2}\right)^{-1} \frac{\partial D}{\partial l} \tag{3}$$

Finally, principal curvature analysis is evaluated to reject keypoints that are located at poorly defined edges, which are consequently highly unstable to noise. This is particulary necessary for the difference of Gaussian function because most of the detected keypoints are located at edges. The bigger the principal curvature, the poorer is its edge. Equation (4) shows how the principal curvature is computed (and rejected if it is above a pre-established threshold).

$$\frac{\left(\frac{\partial D}{\partial x^2} + \frac{\partial D}{\partial y^2}\right)^2}{Det(H)} \le Threshold \tag{4}$$

where

$$H = \begin{bmatrix} \frac{\partial D}{\partial x^2} & \frac{\partial D}{\partial x \partial y} \\ \frac{\partial D}{\partial y \partial x} & \frac{\partial D}{\partial y^2} \end{bmatrix}$$

(5)

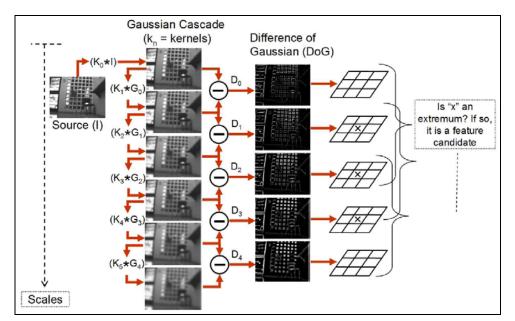

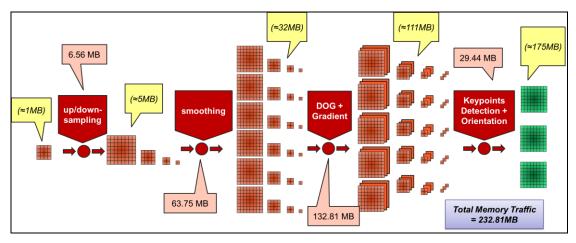

Fig. 3 shows a block diagram representing the main operations of the SIFT algorithm.

Fig. 3: Block diagram representing the main operations of SIFT.

We consider the following parallelization strategy, divided in four stages:

- a) Image upsampling and downsampling

- b) Image smoothing

- c) Difference of Gaussians and gradient

- d) Keypoint detection and orientation

The granularity of parallelization is in general decided based on hardware peculiarities, we describe here parameters chosen for a GPU prototype implementation. In a) we create an upscaled image (2:1) and two downscaled images (1:2), (1:4). The parallelization strategy employs as many parallel work units as pixels in each of the output images. Note that multiple work units can be in general grouped in a single parallel thread depending on the peculiarities of the target hardware. For GPUs employing the smallest work unit and the highest number of threads achieves the best results, so we create as many threads as pixels. Also note that scaling independent images can also be done in parallel.

In b) we apply Gaussian filtering as described by equations 1). In c) we compute the DoG (equation 2) and the gradient (), while in d) we accept/reject candidate features through the checks described by equations 3) and 4). The parallelization scheme for all these kernels follows the same pixel-level partitioning.

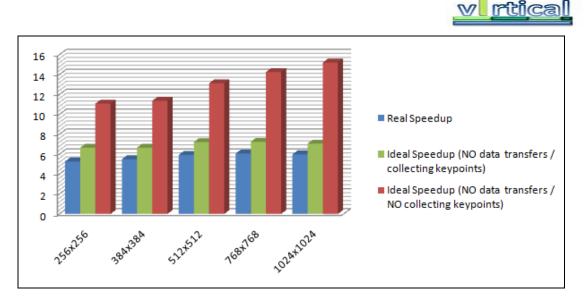

*Fig. 4* shows the speedup results achieved on the target GPU for the SIFT-parallel algorithm, for increasing input image sizes (on the x-axis). We show three different bars. The blue bars represent the speedup obtained against the original OpenCV SIFT function running on the CPU when the whole algorithm is running as we described it above. The green bars represent the speedup obtained when we neglect the cost for moving data back and forth from the CPU space to the GPU space (e.g., what we could achieve if we could iterate the procedure over multiple input images and hide the transfer latency with double buffering techniques). Finally, the red bars show the speedup that can be obtained when we do not run the last kernel (keypoint detection).

Both green and red bars show improvements against the blue bars. In particular, the keypoint detection kernel proves to be the bottleneck in the scalability of the SIFT-parallel algorithm. The main performance blockers for this parallelization scheme are two:

- the presence of conditional instructions, which are in particular used heavily in the keypoint detection stage and which is well known to be detrimental to GPGPU programs performance

- ii. the very significant amount of data moved inside the kernels between global and local GPU memories. Figure 5 reports the size of memory transfers issued in each of the kernels in SIFT-parallel. It is possible to notice that overall there is a huge amount of data being transferred from global to local memory in GPU clusters. A better grouping of work units into parallel threads can help reducing the overall size of these transfers.

Fig. 4: Speedup results for the SIFT-parallel algorithm.

Fig. 5: Memory traffic due to data movements inside kernels in SIFT-parallel.

# 3.2.3.2. SURF

To understand the acceleration opportunities for the SURF application we analyze the implementation available in the OpenCV library running on top of Android 2.3.3 on the DragonBoard. We execute a series of tests on the sequence "freiburg1\_desk", extracted from the dataset described in **[Low04]**. From the original frame size (640x480) we obtained two scaled frame sets (400x300 and 320x240), that we used to assess the algorithm behavior. Figure 6 shows the flat profiles obtained through gprof and android-ndk-profiler. On the top part of the figure (a) we show the profile for frames containing from few tens up to two hundred features. On the bottom part of the figure (b) we show the profile for frames containing eight hundred to one thousand features. The functions implementing the three main stages of the SURF algorithm (see SURF) are:

cv::SURFBuildInvoker::operator() where the pyramid of Gaussian-filtered images is created (see Algorithm 1)

- cv::SURFFindInvoker::operator() where maxima of the determinant of the Hessian matrix are computed

- cv::SURFInvoker::operator() where the descriptor of the extracted keypoints is computed.

It is possible to see that most of the time is spent in smoothing images through Gaussian filtering, as we already observed with SIFT. The second most important contribution to overall execution time is descriptor creation, which clearly has a linear dependence with the number of features found in the target image.

| $\begin{array}{c} \%  {\rm c} \\ {\rm time} \\ 66.63 \\ 24.79 \\ 4.29 \\ 2.97 \\ 0.44 \\ 0.33 \end{array}$ |           | $_{ m seconds}$ | <pre>name<br/>cv::SURFBuildInvoker::operator()<br/>cv::SURFInvoker::operator()<br/>void cv::resizeArea_&lt;<br/>cv::SURFFindInvoker::operator()<br/>cv::integral_8u32s(<br/>void cv::resizeAreaFast_&lt;</pre> |

|------------------------------------------------------------------------------------------------------------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                            |           |                 | (a)                                                                                                                                                                                                            |

| % с                                                                                                        | umulative | self            |                                                                                                                                                                                                                |

| time                                                                                                       | seconds   | seconds         | name                                                                                                                                                                                                           |

| 47.64                                                                                                      | 32.00     | 32.00           | cv::SURFInvoker::operator()                                                                                                                                                                                    |

| 39.08                                                                                                      | 58.25     | 26.25           | cv::SURFBuildInvoker::operator()                                                                                                                                                                               |

| 9.84                                                                                                       | 64.86     | 6.61            | void cv::resizeArea_ <                                                                                                                                                                                         |

| 1.91                                                                                                       | 66.14     | 1.28            | cv::SURFFindInvoker::operator()                                                                                                                                                                                |

| 0.60                                                                                                       | 66.54     | 0.40            | cv :: phase (                                                                                                                                                                                                  |

| 0.31                                                                                                       | 66.75     | 0.21            | void cv::resizeAreaFast_ <                                                                                                                                                                                     |

|                                                                                                            |           |                 | (b)                                                                                                                                                                                                            |

Fig. 6: Execution time profile for SURF. a) profile from frames with up to 200 features. b) profile from frames with 800 to 1000 features.

| Algorithm 1 SURF: filtraggio della piramide gaussiana.                  |  |  |

|-------------------------------------------------------------------------|--|--|

| Require: integral image: sum                                            |  |  |

| Require: array of layers' info: layers                                  |  |  |

| 1: for all $l \in layers$ do                                            |  |  |

| 2: for $i = 0 \rightarrow l.$ octave. rows do                           |  |  |

| 3: $u \leftarrow i * l.$ octave.step                                    |  |  |

| 4: for $j = 0 \rightarrow l.$ octave.cols do                            |  |  |

| 5: $v \leftarrow j * l.$ octave.step                                    |  |  |

| 6: $(dx, dy, dxy) \leftarrow \text{Haar}(sum, u, v, l. \text{pattern})$ |  |  |

| 7: $l.dets(i, j) \leftarrow dx * dy - 0.81 * dxy * dxy$                 |  |  |

| 8: $l.\operatorname{traces}(i,j) \leftarrow dx + dy$                    |  |  |

| 9: end for                                                              |  |  |

| 10: end for                                                             |  |  |

| 11: end for                                                             |  |  |

From these observations the parallelization strategy can be designed as follows:

- Keypoint detection: octaves are traversed sequentially in the original application, but for each of them the computation of the trace and determinant of the Hessian matrix can be executed in parallel for every point in that level, as well as the search for maxima and space-scale interpolation;

- Orientation: the dominant direction can be computed in parallel for every keypoint. Moreover, for each keypoint it is possible to parallelize wavelet filtering and response accumulation in the point of interest neighborhood;

- Descriptor computation: every sub-region of every descriptor can be independently

extracted in parallel over multiple threads (synchronization is needed), to determine the

values of the derivative in every key point of the sub-region. The following normalization

stage can also be executed in parallel over multiple features.

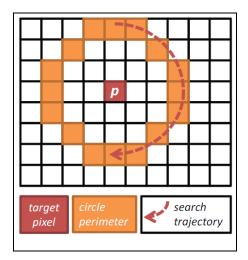

#### 3.2.3.3. FAST

FAST **[Ros10]** is a corner detection algorithm that first analyzes all points in the image, and compares the intensity value of each point p with all the sixteen points on the circle of radius 3 and center p (see *Fig. 7*). p is classified as a corner if there exists a set of contiguous pixels within the circle that are all brighter (minimum) or darker (maximum) of p (with a tolerance threshold). The number of contiguous pixels and the threshold value are both algorithm parameters; typical values are respectively 9 and 20.

Fig. 7: FAST access pattern.

Given an N\*M input image, the algorithm generates an output vector whose size is N\*M\*3, containing the coordinates of the corner points and a score. The latter is used in a subsequent non-maxima suppression stage, which merges multiple pixels belonging to the same corner. Finally, a keypoint detection pass detects relevant features. The core kernel performs most of the computation and it exhibits data-parallelism at the pixel level.

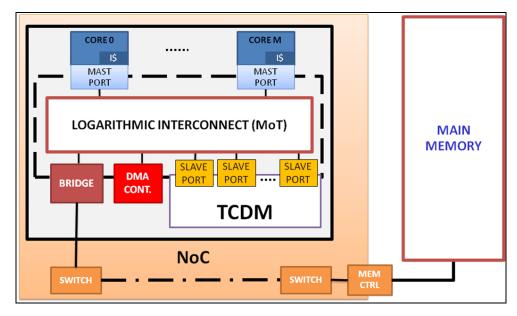

To estimate the acceleration opportunities for our parallel FAST algorithm we design a prototype implementation for a cluster of the GPPA, for which we developed a SystemC virtual platform. The block diagram for a cluster of the GPPA is shown in *Fig. 8*.

Fig. 8: Block diagram of the single-cluster GPPA used for the experiments.

A cluster consists of a configurable number (up to 16) of RISC32 processors with private instruction caches. Processors are interconnected through a low-latency, high-bandwidth logarithmic interconnect, and communicate through a fast multi-banked, multi-ported L1 scratchpad memory (Tightly-Coupled Data Memory – TCDM). The number of memory ports in the TCDM is equal to (a multiple of) the number of banks to allow concurrent accesses to different banks. Conflict-free TCDM accesses have two-cycles latency.

Scaling to larger core counts in this architectural template is achieved by interconnecting several clusters through a NoC, to which we also connect a memory controller to the main memory, where program code and data are originally stored. The table below summarizes the main architectural parameters for our virtual platform.

| ARM v6 Cores          | (up to) 16 | TCDM banks       | 32        |

|-----------------------|------------|------------------|-----------|

| I\$ <sub>i</sub> size | 1 KB       | TCDM size        | 256 KB    |

| I\$ <sub>i</sub> line | 4 words    | MAIN mem latency | 50 cycles |

| t <sub>hit</sub>      | 1 cycle    | MAIN mem size    | 256 MB    |

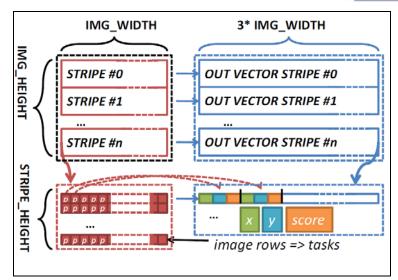

To match these parameters, parallel units of work in FAST are designed to process an entire image row. We consider different sizes for the input images: 64x64, 128x128, 256x256 and 512x512 pixels. As such, the granularity of parallel work units doubles with the input size. However, due to the limited size of the L1 memory (TCDM) it is not possible to store the whole dataset therein. We thus split the image into stripes, and process them one after the other. We adopt a double buffering technique to overlap computation and DMA transfers from the global memory.

Fig. 9: Fast-parallel implementation.

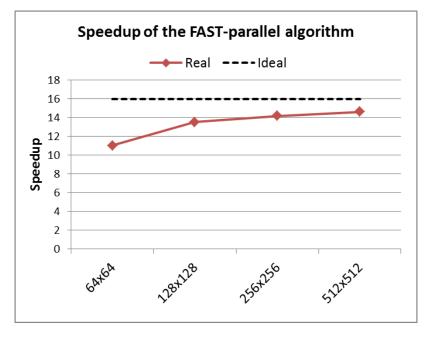

The parallelization scheme is schematically represented in *Fig. 9. Fig. 10* shows the speedup of the parallelized algorithm compared to the sequential version for different image sizes. A considerable speedup is achieved even for small images (11× for a 64x64 image, with each thread only processing 64 pixels) and we reach almost ideal speedup for bigger input sets (256x256 and 512x512), thus confirming the scalability of our parallelization scheme.

Fig. 10: Speedup of the FAST-parallel benchmark for different image sizes.

# 4. Memory system opportunities

Concerning the memory system opportunities, we have identified two different design issues in multicore systems that can help on obtaining the aforementioned target objectives described in

the introduction: cache coherence protocols, (that manage shared objects between cores of the CMP), and compression (for a power consumption and execution time efficient system).

The cache coherence problem arises when copies of the data are found at several private caches associated to the cores, being reachable at the same time by two or more cores, are modifiable by some of them. The cache coherence protocol must guarantee coherence of the data through the entire system which means deciding how and when a single core is granted permission to modify data and ensuring that subsequent readings of the written data by other cores will attain updated copies of the modified data (multiple readers). To do so, different cache coherence mechanisms can be applied. Commonly, these mechanisms introduce certain overhead in terms of either coherence traffic issued or storage resources required, which can significantly penalize performance, increasing the execution time of the running applications as well as power consumption. The current trend to increase the number of cores into CMP and MPSoC systems further aggravates this problem, jeopardizing the scalability of the coherence mechanisms. In brief, the cache coherence protocol does not scale, due to its resource overheads and its indirection when accessing data (access latency is increased).

On the other hand, a different approach to tackle the coherence problem has recently been proposed (**[Cues11]**, **[Har09]** and **[Kim10]**), consisting on removing coherence maintenance for those data objects (memory blocks) that do not need it, either because they are not shared (private to one core) or because they are shared but never written by any core. This approach requires the use of effective mechanisms to identify data blocks that do not need coherence maintenance, which in turn may introduce certain overhead. Anyway, the success and suitability of the selected coherence mechanism will strongly depend on both the architectural context of the system it is being applied to and the sharing patterns of the applications running on the system.

Therefore, as a first step in the exploration of cache coherence protocols in the virtical project, a detailed analysis of the sharing patterns of the applications to be supported is needed, in order to identify opportunities of applying one or another cache coherence mechanism together with different coherence optimization techniques.

At the same time, in the virtical project, reducing power consumption is of high relevance. In the final system a NoC will be developed connecting all the key components. When running the coherence protocol, the NoC will be in charge of transmitting large amounts of data, mainly memory blocks between memory resources (L1s, L2s, directory structures, memory controllers). Data transferred in the NoC can consume a significant percentage of the power of the system, more significant as the system will increase in size.

In several previous works, different data compression mechanisms are proposed and analyzed. In those works, the impact of NoC traffic in system power and execution overhead can be significantly reduced. In this deliverable we present a detailed analysis of the traffic generated by the analyzed applications over the NoC, in the context of the vIrtical project. The main aim is to identify compression opportunities so to select the best mechanisms that will optimize power reduction when focusing on the data traffic over the NoC. It is important to note that we focus on

NoC-data compression opportunities and not on storage compression opportunities. Thus, data is expected to be compressed and uncompressed when entering and leaving the NoC transmission respectively.

The remainder of this section is organized as follows: first we will give an overview of the capturing methodology used to obtain the data analyzed; secondly we will focus first on sharing patterns and later on, on compression opportunities detailing specific methodology particularities and showing our analysis results; finally some conclusions will be derived of the previous analysis and directions for next year research within the project for compression and coherence protocols will be given.

# 4.1. Analysis Methodology

Both sharing patterns and NoC-data compression opportunities must be analyzed under the same premises and thus they must share the applied methodology and tools. However, they also differ in several aspects. An analysis framework has been built in any case to make these analyses possible. In this section we show the main characteristics of such framework.

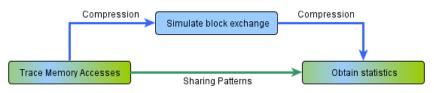

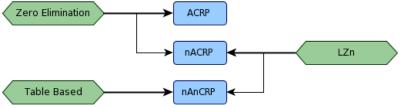

The steps followed to analyze both issues are similar as can be seen in *Fig. 11*. First of all, in both cases, we trace memory accesses requested by the cores when running real applications. For the NoC-data compression analysis we perform a second step aimed at simulating the transfer over the NoC of data blocks included in the previously traced memory accesses over the NoC. Finally in both cases, we obtain statistics for the previously obtained traces.

Fig. 11: Analysis Methodology Scheme.

## 4.1.1. Target System

The target system considered in the project is a heterogeneous multiprocessing system with a NoC connecting the main processing units, a GPPA to enhance performance and the main memory. The ARM architecture is defined as the target processing host, more precisely ARM's big.LITTLE architecture. It consists of one dual-core Cortex-A15 MPCore and one dual-core Cortex-A7 MPCore connected using the ARM CoreLink CCI-400 as described in Deliverable 1.2.

We use a simplified version made of a quad-core Cortex-A15 MPCore. The trade-off between complexity and accuracy makes this option more suitable. Conclusions obtained with the quad-core Cortex-A15 MPCore can be extrapolated to its big.LITTLE counterpart with acceptable precision. Furthermore, big.LITTLE has two different working modes, either only Cortex-A15 or

Cortex-A7 processors are awake or they are both working at the same time. When all processors are working at the same time they will not run a parallel application in both of them because they work at different frequencies. Since we are mainly concerned on parallel applications, the use of big.LITTLE is not mandatory.

Other characteristics of the simulated system for compression opportunities are:

- NoC with a 4x4 2D mesh where each core has been simulated as an individual node. In the target system the whole quad Cortex-A15 will be only one node, but in order to model the behavior of caches separating cores was a more suitable option.

- 4 L1 caches (one per core) each with 128 sets, 4 ways and a line size of 64 bytes.

- 1 L2 cache (shared by all the cores) with 512 sets, 16 ways and a line size of 64 bytes. Caches are inclusive (L1 caches' content is included in L2).

- 4 memory controllers located at the corners of the NoC.

- As for messages we have: control messages are 8 bytes long and data message are 72 bytes long; flit size is 4 bytes.

- The switching mechanism is virtual cut-through and the flow control is Stop&Go. The crossbar is allocated at packet level and supports collective communication (although at the moment no broadcast or multicast is being applied).

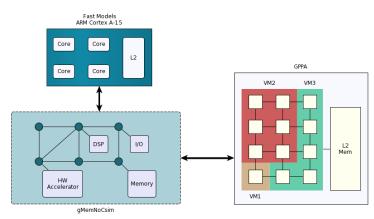

In *Fig.* 12 we can see the simulation target system, with the ARM Cortex-A15, the GPPA and other potential components connected by the NoC. (The figure does not show the 4x4 mesh, instead it shows an irregular topology).

Fig. 12: Simulation target system

## 4.1.2. Simulation Tools

We use ARM FastModels together with our gMemNoCsim tool. Next we describe how these tools are used to model the target system.

ARM FastModels simulator provides out of the box programmer's view models of the ARM processors. It is thus both functionally accurate and easy to use since ARM processors models are already implemented as an Instruction Set Simulator. We use this simulator to model the quad-core Cortex-A15 MPCore part of the target system and to run on top of this the targeted applications.

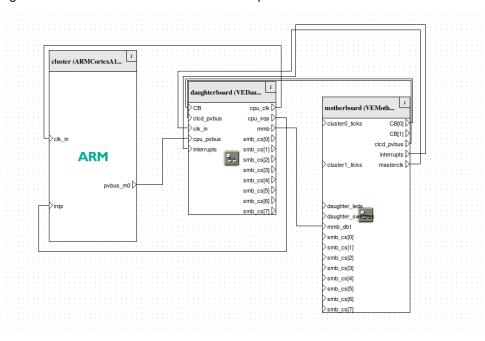

The model of Cortex-A15 provided with FastModels is capable of running basic applications, but it does not cover all the requirements of an operating system, which is needed to evaluate and benchmark parallel applications. We thus use a more complex model also provided with FastModels (namely RTSM-VE Cortex-A15) that allows the simulation of both operating systems and applications. In this RTSM-VE model, as seen on *Fig. 13*, the cores are connected directly to a Versatile Express platform through a 64-bits AXI bus. This platform includes the Motherboard Express uATX, which has been especially designed to support future generations of ARM processors, and the CoreTile Express daughterboard with the on-board DDR2 SDRAM. The motherboard provides the following features:

- Peripherals for multimedia or networking environments.

- All motherboard peripherals and functions are accessed through a static memory bus to simplify access from daughterboards.

- Consistent memory maps with different processor daughterboards simplify software development and porting.

- Supports FPGA and processor daughterboards to provide custom peripherals, or early

access to processor designs, or production test chips.

The daughterboard contains the Cortex-A15 ARM processor model.

Fig. 13: ARM FastModels RTSM-VE model.

On the other hand, gMemNoCsim is a cycle accurate event-driven NoC simulator developed at UPV by the parallel architectures group (GAP), which allows high precision in modeling the key elements of NoCs, including all the key design aspects: as topologies, router, routing algorithms, schedulers and flow control mechanisms. In its current version, gMemNoCsim also models cache coherence protocols on top of the NoC.

gMemNoCsim has the capability of working with synthetic traffic, with real traces or it can be fed on-line with the output of a different simulator. In our case we feed gMemNoCsim with the memory access traces obtained by running the applications on Fast Models. Thus, gMemNoCsim simulates the memory hierarchy (converting memory accesses in memory block accesses flying between L2 cache and main memory over the NoC). This will provide the data needed to analyze compression opportunities.

gMemNoCsim has been enhanced, within the project, to add support for actual data exchange between all levels of the memory hierarchy. Also, tracing capability of gMemNoCsim has been provided to cope with the needs of compression analysis.

#### 4.1.3. Trace Acquisition Methodology

The information that we expect to find on the trace files differs, depending on the focus of the analysis, whether the analysis is made in search of compression opportunities or for sharing pattern analysis. For sharing pattern analysis we need to capture all memory accesses from the cores. In turn, for memory compression opportunities, as communication between L1 and L2 is managed internally by ARM processors, we need to capture all communication between L2 and main memory. In the later we also need to know the memory contents in order to analyze the data transferred.

For sharing pattern analysis our point of interest is the parallel section of the applications, namely the section executed by several cores at the same time. To identify this section we explored the application code looking for the starting point and end point of threads. This was identified with THALES support. To delimit this section and make it recognizable by FastModels we introduce a special *nop* instruction on the application, which is available on the ARM Instruction Set. Therefore, tracing is started when the reserved instruction is fetched and a subsequent appearance of such an instruction determines that the tracing must finish.

On the other hand, compression involves not only shared data but also private data, so limiting the trace acquisition to the parallel section of the applications is no longer mandatory. Nevertheless, beyond that consideration, the traces obtained for sharing pattern analysis are suitable for compression analysis as well, so no different set of traces has been obtained.

FastModels supports the use of a Model Trace Interface (MTI) plug-in that permits us to consistently track the execution of the model. Through implementing an MTI plug-in for tracing memory accesses produced by the cores and adding it to the simulation we are able to trace exactly what we needed in the form that we required. The ARM simulator offers other alternative tracing methods but they would either modify the system behavior when using RTSM-VE model or be prohibitively time consuming.

MTI plug-in provides many different sources to trace, but the more verbose the trace obtained is and the more sources are involved, the more it slows down the simulation. Since it takes billions of instructions to boot a Linux system on FastModels, we need to deactivate the output and minimize the number of sources of the tracing until the starting point of the segment of interest is detected. We have achieved an acceptable compromise solution by capturing only the instructions fetched by the cores until we reach the aforementioned special *nop*, and subsequently tracing loads, stores, and fetches until we get to the ending special *nop*.

The ARM Simulator provides programmer's view models with some limitations. On system simulators there is a trade-off between speed and accuracy: very accurate simulators lack in speed whilst fast simulators cannot be totally accurate. FastModels in particular opts for the execution speed thus lacking some features needed for our analysis, such as:

- Instruction timing: A processor issues a set of instructions (a.k.a a quantum) at the same point on the simulation time, and then waits some amount of time before executing the next quantum, being impossible to determine the right time each individual instruction is executed.

- Bus traffic: bus traffic has several optimizations that make it inaccurate. We were able to deactivate some of those optimizations but not all of them, at the expense of making the simulation far slower and still not accurate to the level required.

- It does not support out-of-order execution and write-buffers as architecturally defined: execution on FastModels is only an approximation to execution of architecture and it must be thus considered.

As mentioned above, traces must be obtained in the exchange of L2 and main memory to be used for compression opportunities analysis, including memory contents. Since we could not find a proper MTI source to trace at this point, we used the traces obtained from FastModels and feed them to gMemNoCsim. gMemNoCsim reproduces the communication between all different levels of the memory hierarchy translating loads and stores into coherent requests to main memory. In turn, main memory contents were obtained in FastModels through the use of CADI debug interface when the starting trace point was detected.

Finally, we describe the trace and memory files format. In the case of FastModels, we need to obtain traces with the information required for coherency modeling, including the core id (to characterize the number of sharers of the block), the address (to identify the block being accessed), the type of access (to classify the block as data or instructions and to discriminate writes from reads) and the data (for compression analysis). Traces obtained using gMemNoCsim must include address (to analyze whether or not address compression can be an interesting technique), and data (the entire block contents to analyze compression opportunities). Source and destination have been included for readability.

Traces obtained from ARM FastModels using the MTI plug-in is as follows:

| core,address,type,data                                     |

|------------------------------------------------------------|

| 0,001ea10c,I,b6f6713c                                      |

| 0,b6f6713c,f,e92d001f                                      |

| 0,bef1de68,s,0020787c                                      |

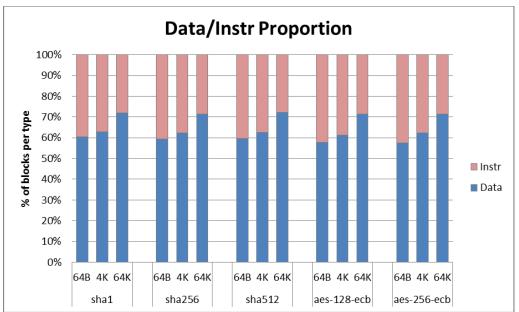

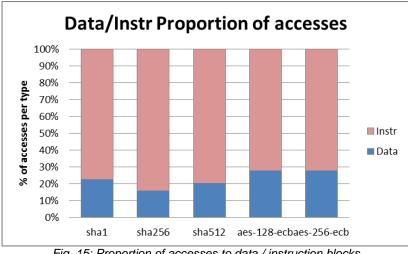

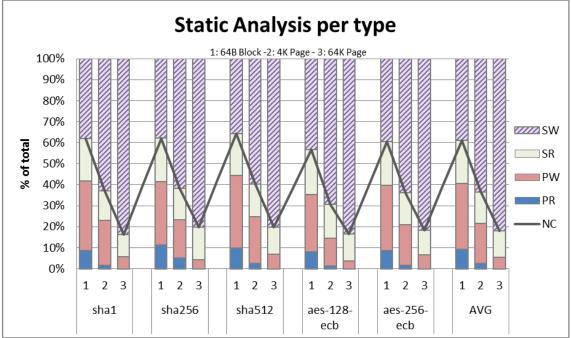

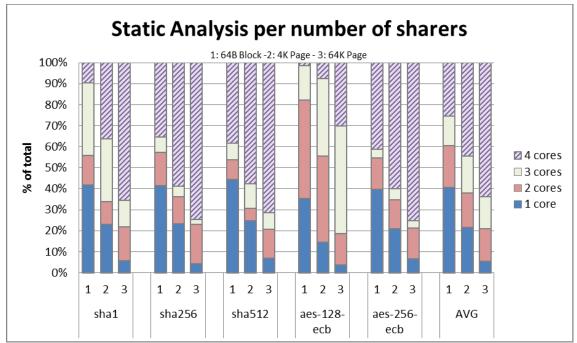

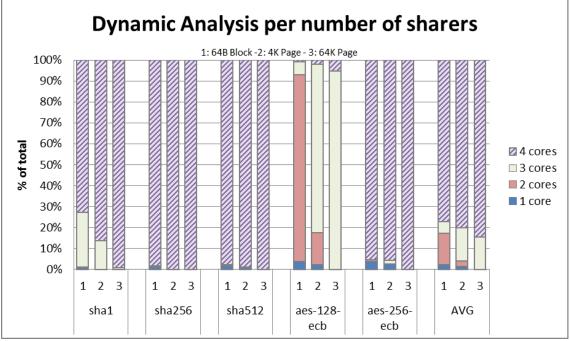

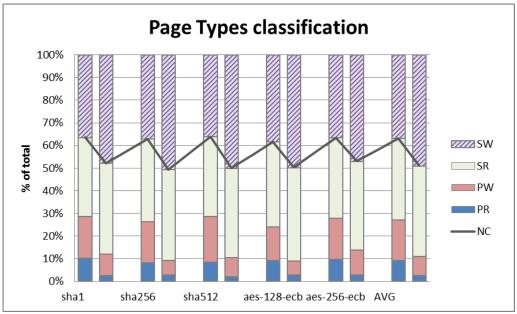

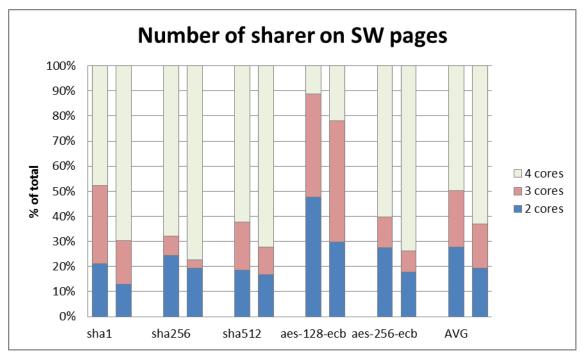

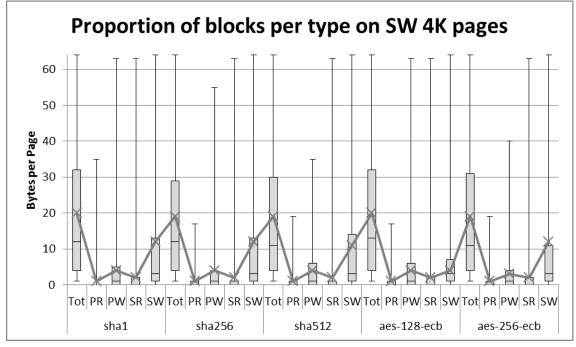

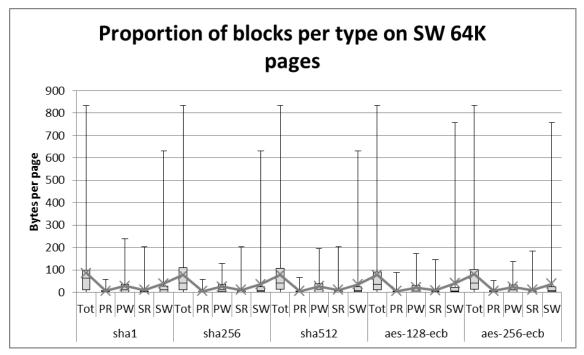

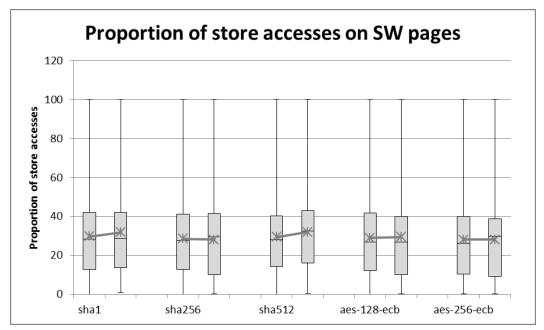

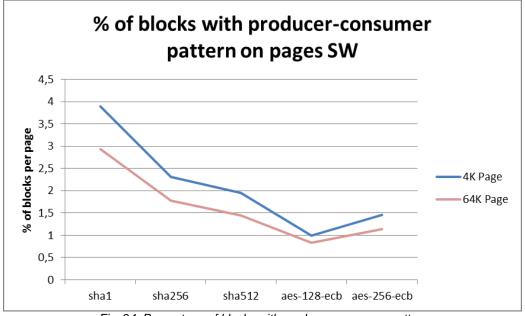

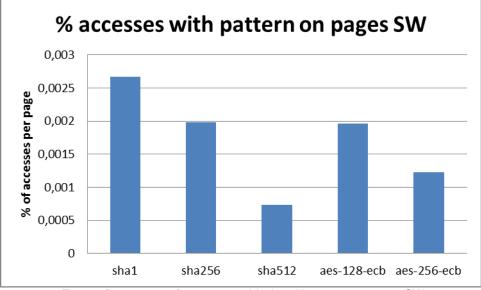

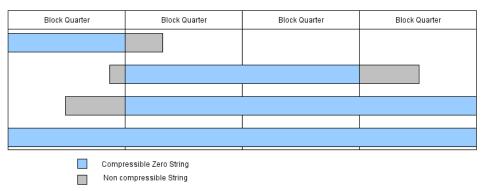

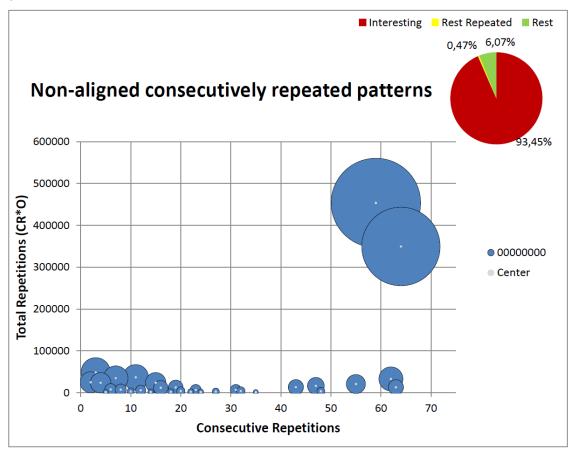

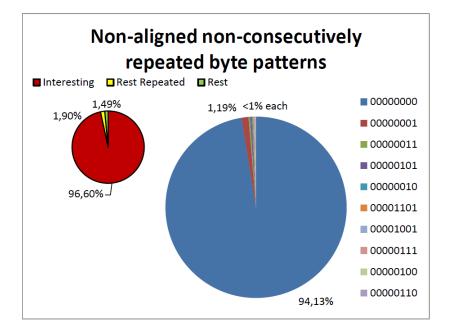

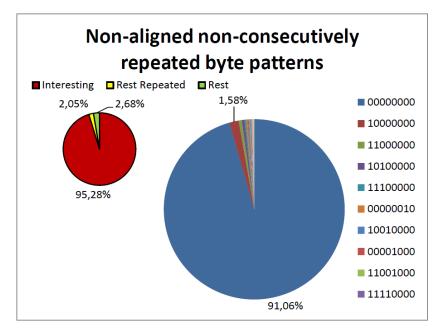

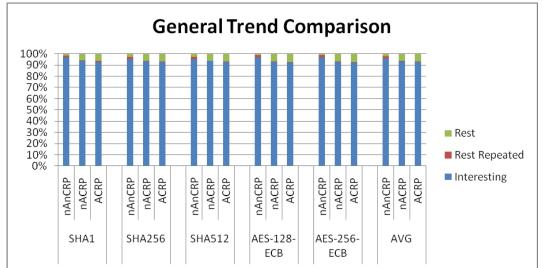

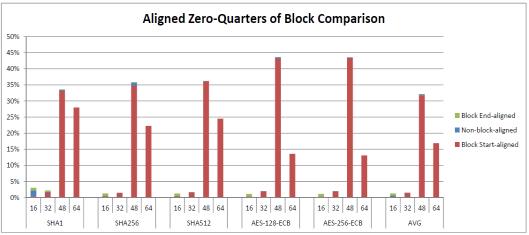

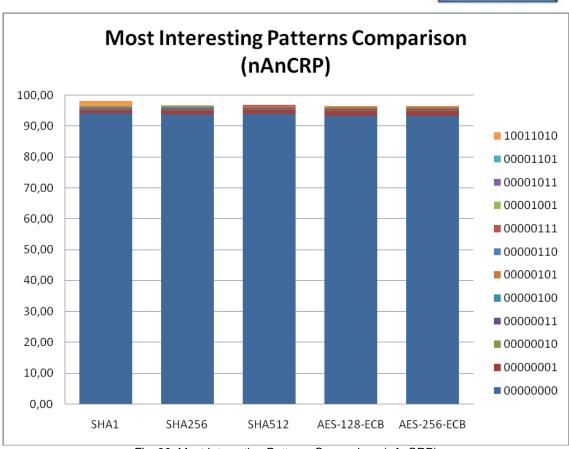

| 0,bef1de10,bs,bef1eef4,bef1ef10,bef1f984,001a0c9c,00000003 |